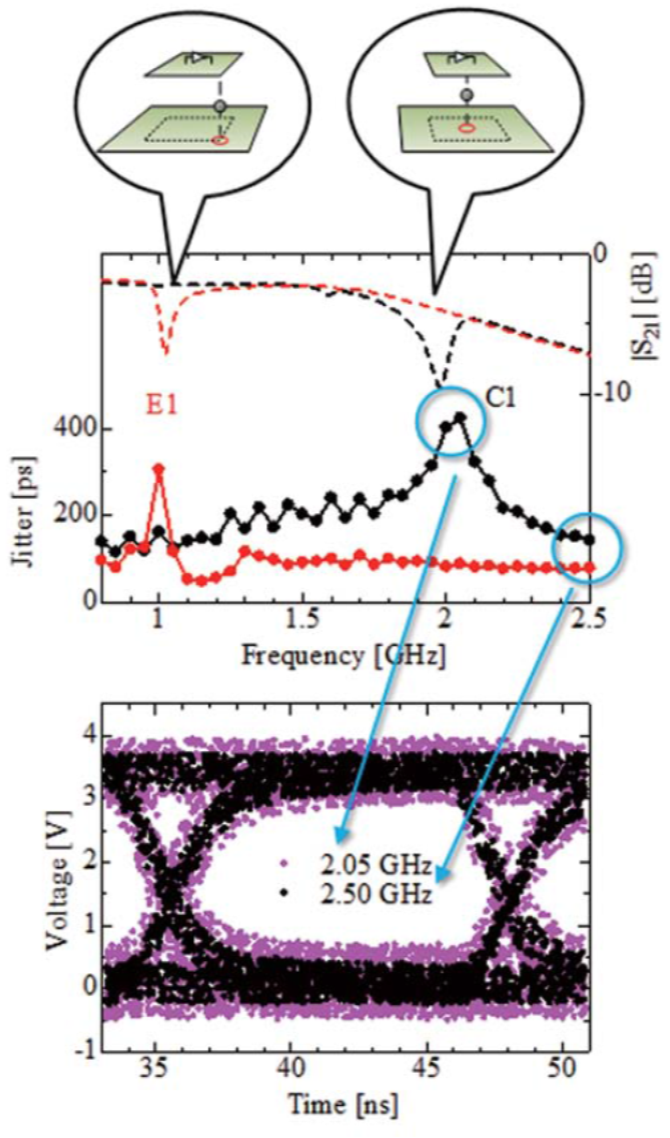

半導体集積回路(LSI) を回路基板上に実装する際の、不要な回路共振と、それによる回路特性の劣化についても研究しています。この共振は、LSI パッケージと回路基板の間に存在する寄生容量によるものです。右図に示すように、CMOS-IC を搭載したパッケージとその回路基板のグラウンド間接続の位置を変更して、電源配線から高周波雑音が流入した際の信号波形のタイミングの揺れ(ジッタ:jitter)を実測すると、パッケージが寄生結合により共振する周波数で信号劣化が観測されます。通常のジッタが約100ps であるのに対して、共振点E1 では306ps、共振点C1 では424ps のジッタとなっています。このような不要共振は、パッケージや基板の設計段階で予測して制御すべき問題で、その共振の抑圧法についても研究しています。