半導体の大規模集積回路(LSI)の回路記述モデルについても研究しています。高速高周波動作を行うディジタルLSIは、その本来の信号処理等の機能を果たすために内部で高速に電流をスイッチングします。その結果発生する高周波の電流ノイズが、周辺のアナログ回路や通信用の高周波回路に干渉を発生し、回路の性能を低下させてしまいます。

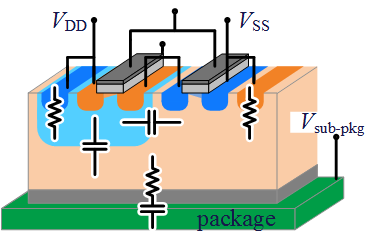

これを防ぐために、LSI そのものを低ノイズ化する設計を行う必要があり、そのため、LSI 自体の高周波電磁特性を記述するマクロモデルが必要とされています。当研究室ではそのための、LECCSモデルと呼ばれるマクロモデルを開発しています。数100万〜数億個のトランジスタを含むLSI の特性をそのままモデル化すると、あまりにもモデルが大規模になりすぎるので、実際の応用回路全体で特性解析を行おうとすると、解析に時間がかかり過ぎで実用的ではありません。そこで、その高周波特性だけをマクロに抽出したモデルがLECCSモデルです。このモデル化の際にも、右図に示すような、半導体チップの内部や半導体基板自体の内部の寄生結合を含めたモデル化に取り組んでいます。